Thermal stability enhancement of low temperature Cu-Cu bonding using metal passivation technology for advanced electronic packaging

By Mu-Ping Hsu 1,Tai-Yu Lin 1, Hua-Jing Huang 2, Chiao-Yen Wang 1, Tsai-Fu Chung 2, Wen-Wei Wu 2 & Kuan-Neng Chen 1

1 Institute of Electronics, National Yang Ming Chiao Tung University, Hsinchu, Taiwan.

2 Department of Materials Science and Engineering, National Yang Ming Chiao Tung University, Hsinchu, Taiwan.

Abstract

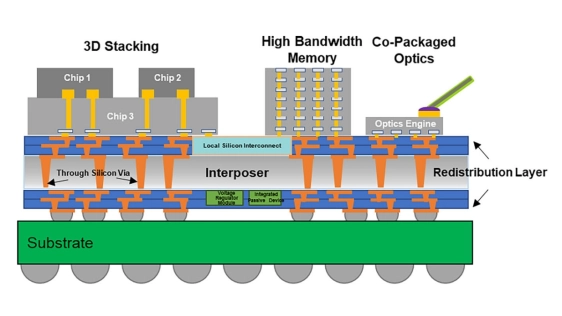

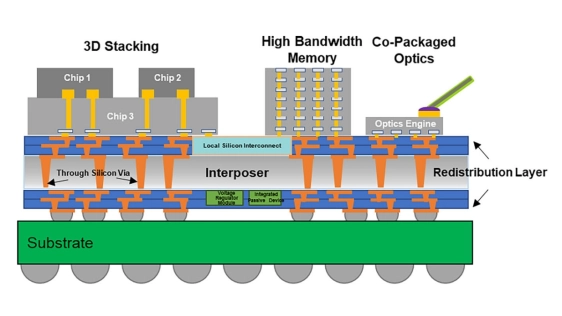

This work investigates the thermal stability of Cu-Cu bonding using a thin Ag passivation layer in applications targeting advanced packaging. Conventional Cu-Cu bonding often requires elevated temperatures (≥250 °C) that can exacerbate thermal stress and limit process flexibility, making multi-chip stacking more challenging. By introducing a 3 nm Ag passivation layer, we demonstrate reliable bonding at lower temperatures with improved durability against high-humidity and high-temperature environments, as confirmed by both Highly Accelerated Stress Tests (HAST) and burn-in measurements. In-situ transmission electron microscopy (TEM) and 4D-STEM strain mapping reveal that Ag diffusion along Cu grain boundaries not only retards abnormal grain growth but also reduces interfacial void formation at elevated temperatures. These enhancements collectively maintain a stable interface and superior mechanical strength relative to that for non-passivated Cu-Cu bonding. The results highlight the importance of metal passivation in enabling low-temperature Cu-Cu bonding technologies with robust thermal stability, providing the feasibility for next-generation advanced packaging platforms.

This work investigates the thermal stability of Cu-Cu bonding using a thin Ag passivation layer in applications targeting advanced packaging. Conventional Cu-Cu bonding often requires elevated temperatures (≥250 °C) that can exacerbate thermal stress and limit process flexibility, making multi-chip stacking more challenging. By introducing a 3 nm Ag passivation layer, we demonstrate reliable bonding at lower temperatures with improved durability against high-humidity and high-temperature environments, as confirmed by both Highly Accelerated Stress Tests (HAST) and burn-in measurements. In-situ transmission electron microscopy (TEM) and 4D-STEM strain mapping reveal that Ag diffusion along Cu grain boundaries not only retards abnormal grain growth but also reduces interfacial void formation at elevated temperatures. These enhancements collectively maintain a stable interface and superior mechanical strength relative to that for non-passivated Cu-Cu bonding. The results highlight the importance of metal passivation in enabling low-temperature Cu-Cu bonding technologies with robust thermal stability, providing the feasibility for next-generation advanced packaging platforms.

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- Thermal Issues Related to Hybrid Bonding of 3D-Stacked High Bandwidth Memory: A Comprehensive Review

- Ammonia Plasma Surface Treatment for Enhanced Cu–Cu Bonding Reliability for Advanced Packaging Interconnection

- Die-Level Transformation of 2D Shuttle Chips into 3D-IC for Advanced Rapid Prototyping using Meta Bonding

- Thermal Implications of Non-Uniform Power in BSPDN-Enabled 2.5D/3D Chiplet-based Systems-in-Package using Nanosheet Technology

Latest Technical Papers

- Affinity Tailor: Dynamic Locality-Aware Scheduling at Scale

- AMMA: A Multi-Chiplet Memory-Centric Architecture for Low-Latency 1M Context Attention Serving

- Exploring the Efficiency of 3D-Stacked AI Chip Architecture for LLM Inference with Voxel

- Epoxy Composites Reinforced with Long Al₂O₃ Nanowires for Enhanced Thermal Management in Advanced Semiconductor Packaging

- Chipmunq: A Fault-Tolerant Compiler for Chiplet Quantum Architectures