EOTPR Fine Pitch Probing for Die-to-Die Interconnect Failure Analysis

By Bernice Zee 1, Wen Qiu 1, Aaron Wai Ken Lee 1, Jesse Alton 2, Thomas White 2, David Kim 2, Martin Igarashi 2

1 Advanced Micro Devices (Singapore) Pte Ltd, Singapore

2 TeraView Limited, United Kingdom

Abstract

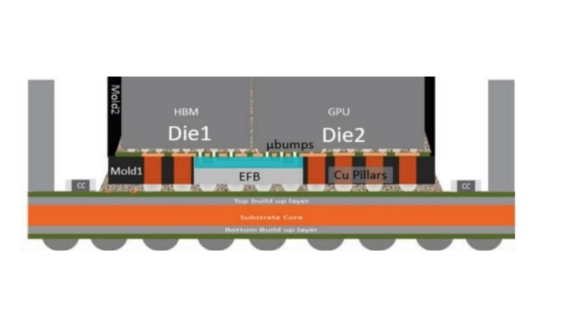

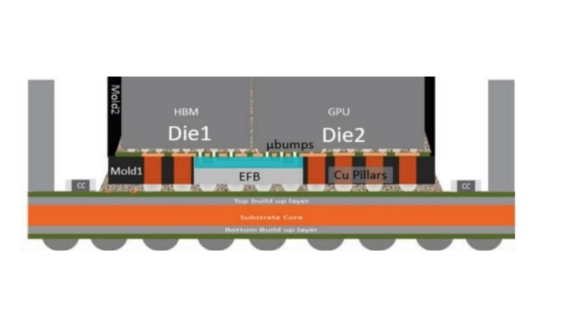

Debug and physical failure analysis (PFA) of heterogeneously integrated semiconductor packages, particularly die-to-die (D2D) input/output (I/O) type fails, has become very challenging due to the lack of direct access to the I/Os from the package substrate to do static open/shorts fault isolation and limited test program granularity to determine which location along the D2D interconnect trace is failing. Thus, a suitable electrical fault isolation technique is required to ensure high success rate for root cause analysis. This paper discusses how EOTPR is used to isolate defects on a D2D interconnect trace of a chiplet advanced packaging using local silicon bridge with reasonable accuracy. Minimal sample preparation was needed to expose the I/O bumps for probing, thus minimizing the risk of artifacts that may cause the defect to be lost. A case study will demonstrate the successful application of the technique.

Debug and physical failure analysis (PFA) of heterogeneously integrated semiconductor packages, particularly die-to-die (D2D) input/output (I/O) type fails, has become very challenging due to the lack of direct access to the I/Os from the package substrate to do static open/shorts fault isolation and limited test program granularity to determine which location along the D2D interconnect trace is failing. Thus, a suitable electrical fault isolation technique is required to ensure high success rate for root cause analysis. This paper discusses how EOTPR is used to isolate defects on a D2D interconnect trace of a chiplet advanced packaging using local silicon bridge with reasonable accuracy. Minimal sample preparation was needed to expose the I/O bumps for probing, thus minimizing the risk of artifacts that may cause the defect to be lost. A case study will demonstrate the successful application of the technique.

Keywords: chiplet packaging, die-to-die interconnect failure analysis, electrical fault isolation, electro-optical terahertz pulse reflectometry fine pitch probing, heterogeneous integration, physical failure analysis, sample preparation, silicon bridge

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- Fast and Accurate Jitter Modeling for Statistical BER Analysis for Chiplet Interconnect and Beyond

- Defect Analysis and Built-In-Self-Test for Chiplet Interconnects in Fan-out Wafer-Level Packaging

- Probeless Fault Isolation Capability for 2.5D/3D Chiplet Die-to-Die Interconnect

- Analysis Of Multi-Chiplet Package Designs And Requirements For Production Test Simplification

Latest Technical Papers

- Affinity Tailor: Dynamic Locality-Aware Scheduling at Scale

- AMMA: A Multi-Chiplet Memory-Centric Architecture for Low-Latency 1M Context Attention Serving

- Exploring the Efficiency of 3D-Stacked AI Chip Architecture for LLM Inference with Voxel

- Epoxy Composites Reinforced with Long Al₂O₃ Nanowires for Enhanced Thermal Management in Advanced Semiconductor Packaging

- Chipmunq: A Fault-Tolerant Compiler for Chiplet Quantum Architectures