CarbonPATH: Carbon-aware pathfinding and architecture optimization for chiplet-based AI systems

By Chetan Choppali Sudarshan, Jiajun Hu, Aman Arora, and Vidya A. Chhabria

Arizona State University

Abstract

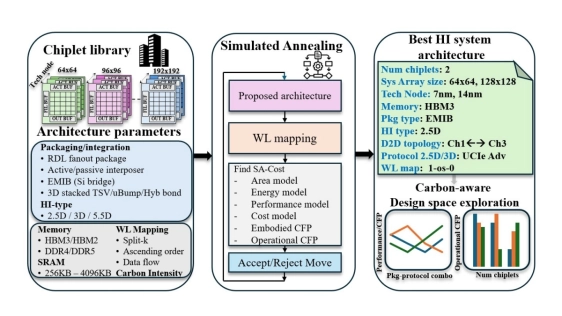

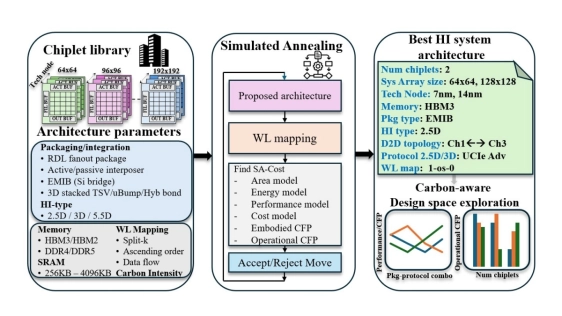

The exponential growth of AI has created unprecedented demand for computational resources, pushing chip designs to the limit while simultaneously escalating the environmental footprint of computing. As the industry transitions toward heterogeneous integration (HI) to address the yield and cost challenges of monolithic scaling, minimizing the carbon cost of these complex HI systems becomes critical. To fully exploit HI, a co-design approach spanning application, architecture, chip, and packaging is essential. However, this creates a vast design space with competing objectives, specifically the trade-offs between performance, cost, and carbon footprint (CFP) for sustainability. CarbonPATH is an early-stage pathfinding framework designed to address this multi-objective challenge. It identifies optimized HI systems by co-designing workload mapping, architectural parameters, and packaging technologies, while treating sustainability as a first-class design constraint. The framework accounts for a wide range of factors, including compute and memory sizes, chiplet technology nodes, communication protocols, integration style (2D, 2.5D, 3D), operational CFP, embodied CFP, and interconnect type. Using simulated annealing, CarbonPATH explores this high-dimensional space to identify solutions that balance traditional metrics against environmental impact. By capturing interactions across applications, architectures, chiplets, and packaging, CarbonPATH uncovers system-level solutions that traditional methods often miss due to restrictive assumptions or limited scope.

The exponential growth of AI has created unprecedented demand for computational resources, pushing chip designs to the limit while simultaneously escalating the environmental footprint of computing. As the industry transitions toward heterogeneous integration (HI) to address the yield and cost challenges of monolithic scaling, minimizing the carbon cost of these complex HI systems becomes critical. To fully exploit HI, a co-design approach spanning application, architecture, chip, and packaging is essential. However, this creates a vast design space with competing objectives, specifically the trade-offs between performance, cost, and carbon footprint (CFP) for sustainability. CarbonPATH is an early-stage pathfinding framework designed to address this multi-objective challenge. It identifies optimized HI systems by co-designing workload mapping, architectural parameters, and packaging technologies, while treating sustainability as a first-class design constraint. The framework accounts for a wide range of factors, including compute and memory sizes, chiplet technology nodes, communication protocols, integration style (2D, 2.5D, 3D), operational CFP, embodied CFP, and interconnect type. Using simulated annealing, CarbonPATH explores this high-dimensional space to identify solutions that balance traditional metrics against environmental impact. By capturing interactions across applications, architectures, chiplets, and packaging, CarbonPATH uncovers system-level solutions that traditional methods often miss due to restrictive assumptions or limited scope.

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- CHICO-Agent: An LLM Agent for the Cross-layer Optimization of 2.5D and 3D Chiplet-based Systems

- FoldedHexaTorus: An Inter-Chiplet Interconnect Topology for Chiplet-based Systems using Organic and Glass Substrates

- AuthenTree: A Scalable MPC-Based Distributed Trust Architecture for Chiplet-based Heterogeneous Systems

- Business Analysis of Chiplet-Based Systems and Technology

Latest Technical Papers

- Affinity Tailor: Dynamic Locality-Aware Scheduling at Scale

- AMMA: A Multi-Chiplet Memory-Centric Architecture for Low-Latency 1M Context Attention Serving

- Exploring the Efficiency of 3D-Stacked AI Chip Architecture for LLM Inference with Voxel

- Epoxy Composites Reinforced with Long Al₂O₃ Nanowires for Enhanced Thermal Management in Advanced Semiconductor Packaging

- Chipmunq: A Fault-Tolerant Compiler for Chiplet Quantum Architectures