In-SoIC ESD Protection for Chiplet-Based 3D Microsystems: Future Research Directions

By Xunyu Li, Runyu Miao, Zijian Yue and Albert Wang

Department of Electrical and Computer Engineering, University of California, Riverside, USA

Abstract

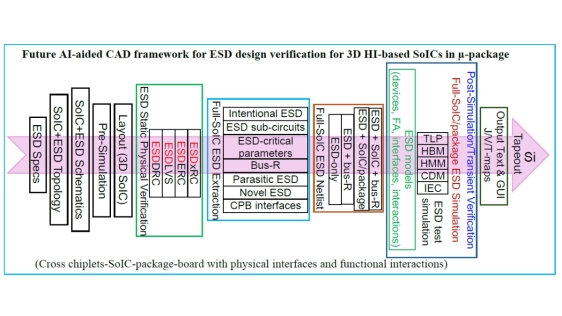

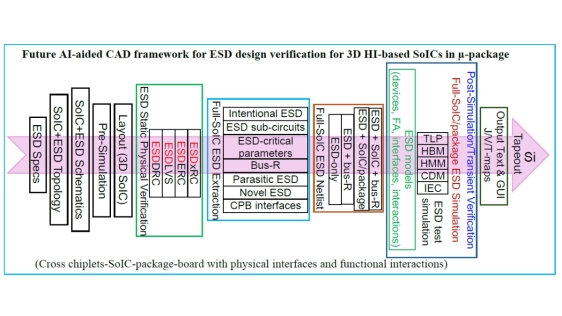

Heterogeneous integration opens a pathway to three-dimensional chiplet-based microsystem chips. Electrostatic discharge reliability is a major challenge to future smart chips featuring rich functionalities and ultra performance, utilizing advanced heterogeneous integration and packaging technologies. This paper discusses emerging challenges and future research directions in developing robust electrostatic discharge protection solutions for future systems-on-integrated-chiplets.

Heterogeneous integration opens a pathway to three-dimensional chiplet-based microsystem chips. Electrostatic discharge reliability is a major challenge to future smart chips featuring rich functionalities and ultra performance, utilizing advanced heterogeneous integration and packaging technologies. This paper discusses emerging challenges and future research directions in developing robust electrostatic discharge protection solutions for future systems-on-integrated-chiplets.

Keywords: electrostatic discharge; ESD protection; chiplet; SoIC; heterogeneous integration

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- Towards efficient ESD protection strategies for advanced 3D systems-on-chip

- On hardware security and trust for chiplet-based 2.5D and 3D ICs: Challenges and Innovations

- Multi-Objective Hardware-Mapping Co-Optimisation for Multi-DNN Workloads on Chiplet-based Accelerators

- Cambricon-LLM: A Chiplet-Based Hybrid Architecture for On-Device Inference of 70B LLM

Latest Technical Papers

- In-SoIC ESD Protection for Chiplet-Based 3D Microsystems: Future Research Directions

- ODIN-Based CPU-GPU Architecture with Replay-Driven Simulation and Emulation

- Chipmunq: Fault-Tolerant Compiler for Chiplet Quantum Architectures

- LEXI: Lossless Exponent Coding for Efficient Inter-Chiplet Communication in Hybrid LLMs

- Link Quality Aware Pathfinding for Chiplet Interconnects