A sneak peek at chiplet standards

By Majeed Ahmad, EDN (September 4, 2023)

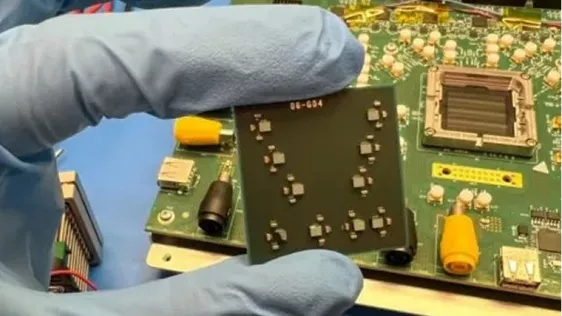

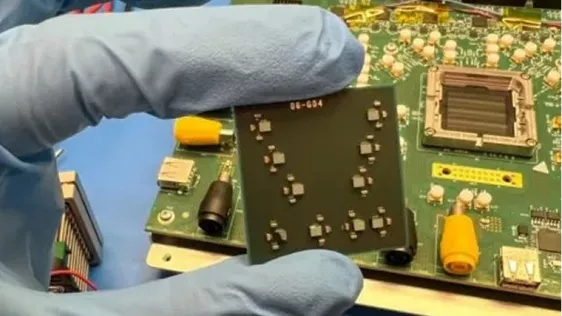

The scaling of system-on-chip (SoC) architectures is hitting the wall, paving the way for die-to-die interconnect in heterogenous single-package systems commonly known as chiplets. But while these chiplet-optimized interconnect technologies are gaining significant traction, they are still in their infancy.

The scaling of system-on-chip (SoC) architectures is hitting the wall, paving the way for die-to-die interconnect in heterogenous single-package systems commonly known as chiplets. But while these chiplet-optimized interconnect technologies are gaining significant traction, they are still in their infancy.

That makes chiplet interconnect standards crucial for the new multi-die semiconductors era. Below is a brief outline of three standards that are considered critical in the present evolution of chiplets. These standards will likely play a vital role in creating an open chiplet ecosystem.

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related News

- 400Gbps/800Gbps IOWN APN demonstration at OFC2024 by multi-vendor products leveraging photonics-electronics convergence device and open standards

- A closer look at Arm’s chiplet game plan

- Opportunities Unleashed by Chiplet Technology: A New Era for the Semiconductor Industry

- Alphawave Semi to Lead Chiplet Innovation, Showcase Advanced Technologies at Chiplet Summit

Latest News

- Xanadu and EV Group partner to build industrial-scale photonic quantum hardware

- AI Optical Interconnect Boom Drives U.S. Firms to Expand Southeast Asia Outsourcing, Opening the Door for Cross-Industry Entrants

- GlobalFoundries accelerates adoption of co-packaged optics for advanced AI data centers with SCALE optical module solution

- TSMC SoIC roadmap targets 2029 chip stacking

- Applied Materials Broadens Advanced Packaging Portfolio with Acquisition of NEXX