The Changing ASICs Landscape: the Shift Toward Chip Disaggregation

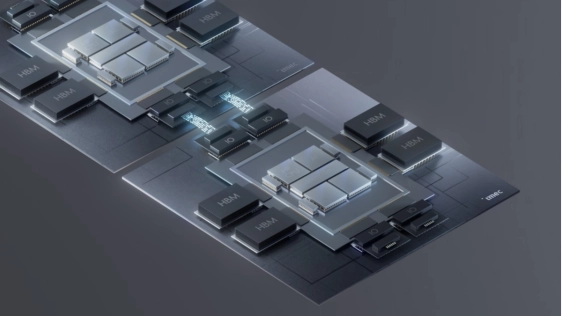

The rapid rise of AI is reshaping the demands placed on silicon. For ASICs, this means workloads are becoming more system-specific while architectures grow increasingly modular and disaggregated. These shifts place greater weight on cross-domain collaboration spanning architecture, packaging, and manufacturing.

For many years, ASICs were designed around relatively stable standards and well-defined functions: video codecs, networking protocols, signal processing pipelines, and so forth. Performance gains largely came from integrating more functionality onto a single monolithic die and relying on process scaling to do the rest.

For many years, ASICs were designed around relatively stable standards and well-defined functions: video codecs, networking protocols, signal processing pipelines, and so forth. Performance gains largely came from integrating more functionality onto a single monolithic die and relying on process scaling to do the rest.

That model is now under pressure. AI workloads are highly diverse, compute-intensive, and tightly coupled to software behavior and system context. A single “best” architecture no longer exists. Instead, performance, power, and cost are determined by how well silicon is tailored to a specific combination of algorithms, data flows, deployment constraints, and operating environments.

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Blogs

- Embracing the Chiplet Journey: The Shift to Chiplet-Based Architectures

- Redefining SoC Design: The Shift to Secure Chiplet-Based Architectures

- Automotive chiplets: The path towards modularity, improved cost structures and supply resilience

- Synopsys and Intel Team Up on the First UCIe-Connected Chiplet-Based Test Chip

Latest Blogs

- The Changing ASICs Landscape: the Shift Toward Chip Disaggregation

- Topology and Data Movement in Multi-Die Design

- How to Streamline Your Advanced Package (Chiplet, 3DIC) Interconnect Designs

- Interface IP: The Keystone for 3D Multi-Die Designs

- Samsung Foundry and Cadence: Accelerating Chiplet Solutions for Physical AI