Chiplet innovation isn’t waiting for perfect standards

Across markets such as AI, high-performance computing (HPC), and automotive, the demand for computational power continues to accelerate. This demand spans everything from compact edge devices to massive data center servers. Traditionally, that capacity was delivered by monolithic systems-on-chip (SoCs) implemented on a single silicon die. While manufacturing trade-offs can ease some pressures, a large die still limits optimization, forcing designers to balance power and performance across the entire chip rather than fine-tuning each function individually.

The problem is structural. Monolithic SoCs have reached physical and economic limits. Reticle size is fixed, yields decline as die size grows, and the cost of large devices is prohibitively high.

The problem is structural. Monolithic SoCs have reached physical and economic limits. Reticle size is fixed, yields decline as die size grows, and the cost of large devices is prohibitively high.

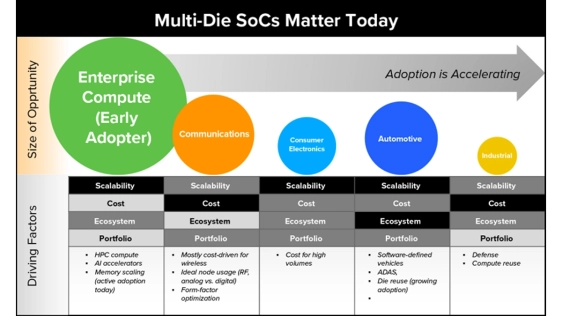

Multi-die systems offer a practical path forward. By breaking a large SoC into smaller chips, teams gain better yields, leverage proven components, and combine diverse process technologies in a single package. Additionally, chiplets can be reused across product lines, improving scalability and reducing cost.

The semiconductor industry has long envisioned chiplets as modular and interoperable, backed by fully proven standards. Companies are not waiting for that vision to materialize fully. They are already moving ahead with chiplet adoption while standards remain in flux.

Why chiplets, and why now?

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Blogs

- How Cadence Is Expanding Innovation for 3D-IC Design

- The Chiplet Center of Excellence sets new standards for the automotive industry

- Marvell Joins Imec Automotive Chiplet Initiative to Facilitate Compute SoCs for Super-human Sensing

- What is a Chiplet, and Why Should You Care?

Latest Blogs

- Addressing AI and Advanced Packaging Challenges with Synopsys 3DIO PHY

- Ultra-high repeatability and ultra-low insertion loss wafer and die-level visible-range E-PIC device characterization using an MPI Corp. probe system, enabled by process optimization from Quantum Transistors

- The Changing ASICs Landscape: the Shift Toward Chip Disaggregation

- Topology and Data Movement in Multi-Die Design

- How to Streamline Your Advanced Package (Chiplet, 3DIC) Interconnect Designs